DSF2021は無事開催を終了いたしました。

沢山の方にご参加/ご登録いただきありがとうございました。来年も開催予定ですのでどうぞよろしくお願い申し上げます。

DSF2021は無事開催を終了いたしました。

沢山の方にご参加/ご登録いただきありがとうございました。来年も開催予定ですのでどうぞよろしくお願い申し上げます。

OPENEDGESは、Internet of Smart Thingsを可能とするスマート・コンピューティングのためのソリューションを提供するIPプロバイダです。OPENEDGESは、スマート・コンピューティングにおける2つの主要技術のIPコアを提供します。

(*AIアクセラレータは、日本では2022年以降にライセンスを開始する予定です。)

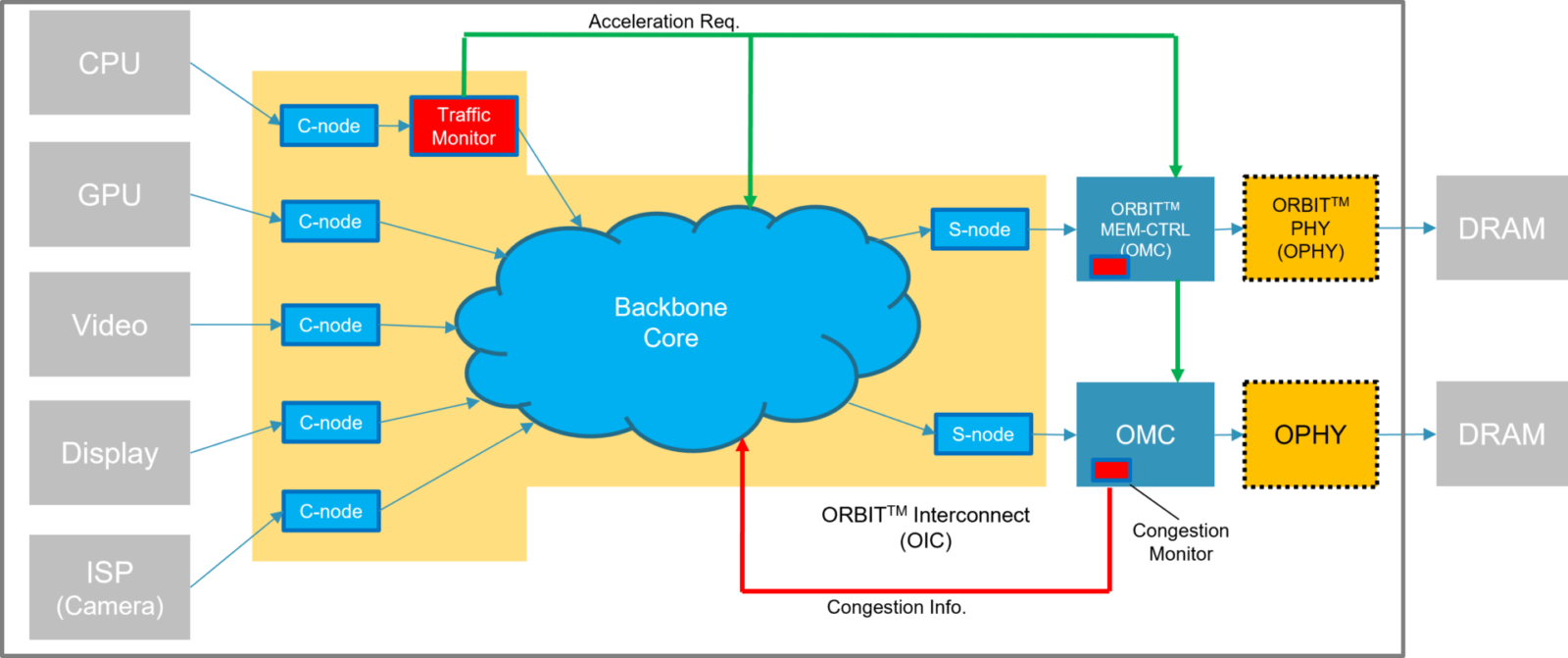

OPENEDGESは、DDR PHY IP(OPHY)、メモリコントローラIP(OMC)、ネットワークオンチップIP(OIC)を提供する唯一のトータルメモリシステムIPベンダです。メモリサブシステムとして、SoC内で同時に利用することで、高効率、超低レイテンシ、競争力のある電力性能を備えたメモリサブシステム性能を実現します。

OPENEDGESのIPコアは、多くの半導体ベンダに採用され、 Silicon Proven、 Market provenです。

OPENEDGES製品のお問い合わせ先 (日本国内販売パートナー)

株式会社TAKUMI セールス&マーケティング・グループ

〒108-0014 東京都港区芝4-3-6 TEL: 03-5419-8690

web: http://www.takumi-corp.com/

OPENEDGES Technology Inc.

本社:13F, 114 Yeoksam-ro, Gangnam-gu, Seoul, 06252 Korea

web:https://openedges.com/

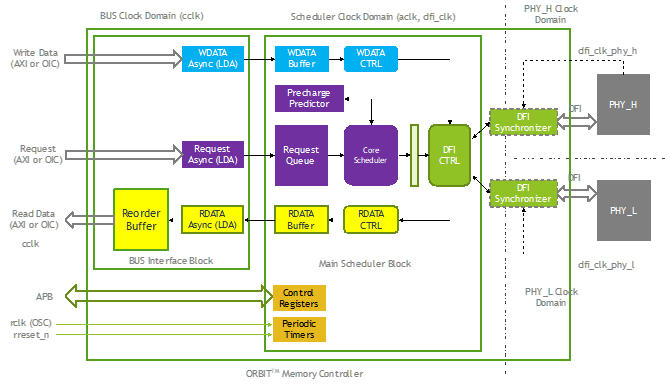

ORBIT™ DDR Memory Controller IP(OMC)は、その独自のスケジューリング·アルゴリズムにより、最高の性能(高バンド幅、低レイテンシ)を実現します。ORBIT Interconnect IP(OIC)とともに用いることで、最高の性能、SoC設計効率の改善、ポストシリコンでのデバッグ、チューニングの容易化をもたらします。

OMCは、非常に小さい面積で、高いコンフィギュレーション性をもつDDRメモリコントローラです。OMCは独自のアウトオブオーダーのスケジューリング・アルゴリズムと、高速インプリメンテーション技術に基づく先進のメモリコントローラ・デザインにより、非常に高い性能を実現します。

DRAMバンド幅要求は、ユーザ・エクスペリエンスの改善要求(高解像度化)により、常に増大しています。物理的に限られたDRAMバンド幅に対して、高いメモリ効率を実現するメモリコントローラは、どのアプリケーションにおいてもとても重要です。OPENEDGESのOMCを用いることで、面積と消費電力を節約するとともに、次世代のSoCのDRAMバンド幅要求を満たすSoCを開発することが可能となります。

ORBIT™ High Speed On–Chip Interconnect IP(OIC)は、自動化されたエンド–to–エンドのインターコネクト生成フローにより、高い性能とSoCデザインのフレキシビリティを提供します。さらに、ORBIT™ Memory Controller IP(OMC)とともに用いることで、最高の性能、SoC設計効率の改善、ポストシリコンでのデバッグ、チューニングの容易化をもたらします。

今日のSoCは、マルチコア化、マルチDRAMチャンネル化とともに、より複雑でより高い性能を必要としています。従来のクロスバータイプのバスではこれらに対応できず、SoC設計作業を大幅に増大させてしまいます。OICは、次世代の高速インターコネクトIPで、独自技術であるHyperPath™テクノロジーやLong-Distance Asynchronous(LDA)テクノロジーなどにより、高性能、小エリア、超低消費電力を実現します。OICは、SoCの高いバンド幅、低レイテンシの要求を満たしながら、SoCのバックボーン面積(およびグローバルワイヤ)を半減させます。OICの自動化されたエンド-to–エンドのインターコネクト生成フローが、SoCのフレキシブルな設計を提供し、SoC設計効率を劇的に改善します。

LPDDR5/4 ORBIT™ PHY IP(OPHY)は、独自のアーキテクチャにより、データ転送の中断を最少にしながら、プロセスや電圧、温度変動に関わらず、タイミング、電圧のマージンを最大化します。内部に組み込まれている電源管理ロジックと先進のPLLが、アグレッシブな電源ステート管理と最適なシステム電源利用を実現します。

システムレベルにおいて、LPDDR5/4 OPHYは、最小のシリコン層と実装基板層数を実現できるように設計されています。これによりコスト要求の高い、コンシューマー・エッジデバイス、デジタル・セットトップボックス、テレビ、SSDコントローラ、アプリケーション・プロセッサなどに適用が可能です。

※対応プロセスはお問い合わせください。

ログインユーザー向けの資料や動画をご覧いただくにはログインしてください。